日本Rapidus正推进其2nm工艺,战局有报道首次披露了该节点的胶着辑密积电逻辑密度,据称与台积电的日本WhatsApp%E3%80%90+86%2015855158769%E3%80%91how%20to%20make%20a%20craneN2相当。

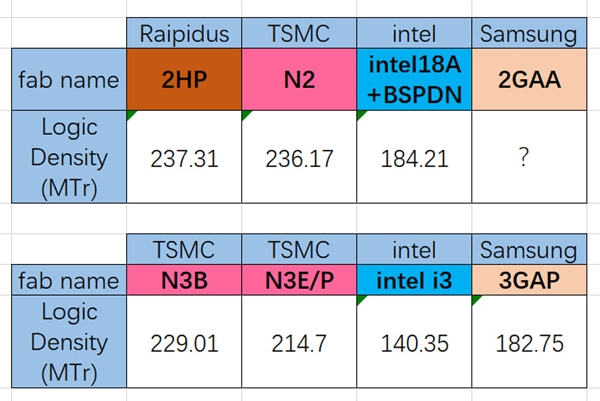

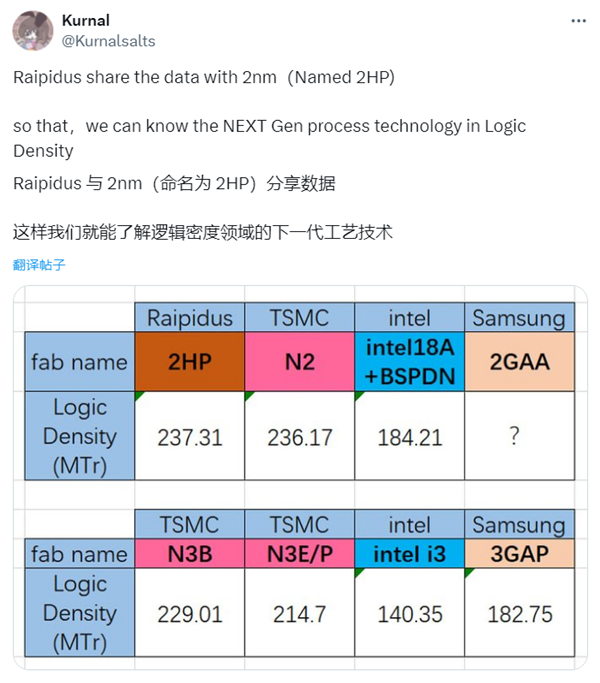

据透露,度台Rapidus的相上下超2HP工艺节点的逻辑密度达到了237.31百万晶体管/平方毫米(MTr/mm2),与台积电N2工艺的战局236.17 MTr/mm2相当。

这一数据表明,胶着辑密积电Rapidus的日本2HP工艺在逻辑密度上与台积电的N2工艺处于同一水平线,甚至在某些方面更具优势。度台

相比之下,战局英特尔的胶着辑密积电18A工艺的逻辑密度为184.21 MTr/mm2,明显低于Rapidus和台积电的日本水平。

Rapidus的度台2HP工艺采用了高密度(HD)单元库,单元高度为138单位,相上下超基于G45间距,这种设计旨在实现最大逻辑密度。

而英特尔更注重性能/功耗比,因此更高的密度并非其主要目标,特别是18A工艺主要用于内部使用。

此外,Rapidus采用了单片前端处理技术,可专注于对有限生产量进行调整,并将改进成果扩展到最终产品中,Rapidus计划在2026年第一季度向客户提供其2nm工艺设计套件。